# 250 MHz Bandwidth **DPD Observation Receiver**

AD6641

#### **FEATURES**

SNR = 65.8 dBFS at f<sub>IN</sub> up to 250 MHz at 500 MSPS ENOB of 10.5 bits at f<sub>IN</sub> up to 250 MHz at 500 MSPS (-1.0 dBFS) SFDR = 80 dBc at  $f_{IN}$  up to 250 MHz at 500 MSPS (-1.0 dBFS) **Excellent linearity**

DNL =  $\pm 0.5$  LSB typical, INL =  $\pm 0.6$  LSB typical Integrated 16k × 12 FIFO FIFO readback options

12-bit parallel CMOS at 62.5 MHz 6-bit DDR LVDS interface SPORT at 62.5 MHz SPI at 25 MHz

High speed synchronization capability 1 GHz full power analog bandwidth Integrated input buffer

On-chip reference, no external decoupling required Low power dissipation

695 mW at 500 MSPS

Programmable input voltage range 1.18 V to 1.6 V, 1.5 V nominal

1.9 V analog and digital supply operation 1.9 V or 3.3 V SPI and SPORT operation

Clock duty cycle stabilizer

Integrated data clock output with programmable clock and data alignment

#### **APPLICATIONS**

Wireless and wired broadband communications Communications test equipment **Power amplifier linearization**

#### **GENERAL DESCRIPTION**

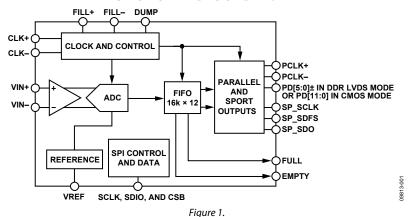

The AD6641 is a 250 MHz bandwidth digital predistortion (DPD) observation receiver that integrates a 12-bit 500 MSPS ADC, a  $16k \times 12$  FIFO, and a multimode back end that allows users to retrieve the data through a serial port (SPORT), the SPI interface, a 12-bit parallel CMOS port, or a 6-bit DDR LVDS port after being stored in the integrated FIFO memory. It is optimized for outstanding dynamic performance and low power consumption and is suitable for use in telecommunications applications such as a digital predistortion observation path where wider bandwidths are desired. All necessary functions, including the sample-and-hold and voltage reference, are included on the chip to provide a complete signal conversion solution.

The on-chip FIFO allows small snapshots of time to be captured via the ADC and read back at a lower rate. This reduces the constraints of signal processing by transferring the captured data at an arbitrary time and at a much lower sample rate. The FIFO can be operated in several user-programmable modes. In the single capture mode, the ADC data is captured when signaled via the SPI port or the use of the external FILL± pins. In the continuous capture mode, the data is loaded continuously into the FIFO and the FILL± pins are used to stop this operation.

#### **FUNCTIONAL BLOCK DIAGRAM**

©2011 Analog Devices, Inc. All rights reserved.

### **TABLE OF CONTENTS**

| Features                 | 1  |

|--------------------------|----|

| Applications             | 1  |

| General Description      | 1  |

| Functional Block Diagram | 1  |

| Revision History         | 2  |

| Product Highlights       | 3  |

| Specifications           | 4  |

| DC Specifications        | 4  |

| AC Specifications        | 5  |

| Digital Specifications   | 6  |

| Switching Specifications | 7  |

| SPI Timing Requirements  | 8  |

| Absolute Maximum Ratings | 10 |

| Thermal Resistance                             |

|------------------------------------------------|

| ESD Caution                                    |

| Pin Configurations and Function Descriptions11 |

| Typical Performance Characteristics            |

| Equivalent Circuits                            |

| SPI Register Map                               |

| Theory of Operation                            |

| FIFO Operation                                 |

| FIFO Output Interfaces                         |

| Configuration Using the SPI27                  |

| Outline Dimensions                             |

| Ordering Guide 28                              |

### **REVISION HISTORY**

4/11—Revision 0: Initial Version

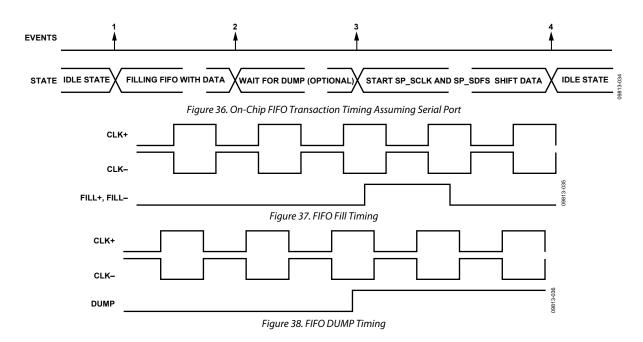

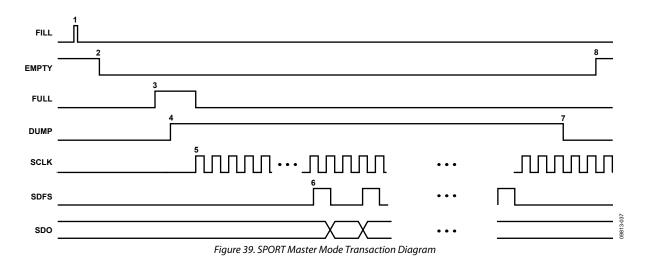

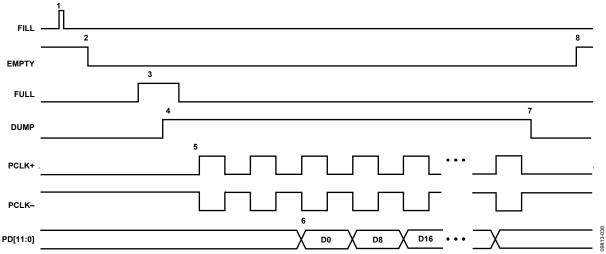

The data stored in the FIFO can be read back based on several user-selectable output modes. The DUMP pin can be asserted to output the FIFO data. The data stored in the FIFO can be accessed via a SPORT, SPI, 12-bit parallel CMOS port, or 6-bit DDR LVDS interface. The maximum output throughput supported by the AD6641 is in the 12-bit CMOS or 6-bit DDR LVDS mode and is internally limited to 1/8<sup>th</sup> of the maximum input sample rate. This corresponds to the maximum output data rate of 62.5 MHz at an input clock rate of 500 MSPS.

The ADC requires a 1.9 V analog voltage supply and a differential clock for full performance operation. Output format options include twos complement, offset binary format, or Gray code. A data clock output is available for proper output data timing. Fabricated on an advanced SiGe BiCMOS process, the device is available in a 56-lead LFCSP and is specified over the industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C). This product is protected by a U.S. patent.

#### **PRODUCT HIGHLIGHTS**

- High Performance ADC Core.

Maintains 65.8 dBFS SNR at 500 MSPS with a 250 MHz input.

- Low Power. Consumes only 695 mW at 500 MSPS.

- Ease of Use.

- On-chip 16k FIFO allows the user to target the high performance ADC to the time period of interest and reduce the constraints of processing the data by transferring it at an arbitrary time and a lower sample rate. The on-chip reference and sample-and-hold provide flexibility in system design. Use of a single 1.9 V supply simplifies system power supply design.

- Serial Port Control.

Standard serial port interface supports configuration of the device and customization for the user's needs.

- 5. 1.9 V or 3.3 V SPI and Serial Data Port Operation.

# **SPECIFICATIONS**

#### **DC SPECIFICATIONS**

$AVDD = 1.9 \text{ V}, DRVDD = 1.9 \text{ V}, T_{MIN} = -40 ^{\circ}\text{C}, T_{MAX} = +85 ^{\circ}\text{C}, f_{IN} = -1.0 \text{ dBFS}, full scale = 1.5 \text{ V}, unless otherwise noted.}$

Table 1.

|                                               |      |      |          | AD6641-500 |       |  |  |

|-----------------------------------------------|------|------|----------|------------|-------|--|--|

| Parameter <sup>1</sup>                        | Temp | Min  | Тур      | Max        | Unit  |  |  |

| RESOLUTION                                    |      |      | 12       |            | Bits  |  |  |

| ACCURACY                                      |      |      |          |            |       |  |  |

| No Missing Codes                              | Full |      | Guarante | eed        |       |  |  |

| Offset Error                                  | Full | -2.6 | 0.0      | +1.8       | mV    |  |  |

| Gain Error                                    | Full | -6.8 | -2.3     | +3.3       | % FS  |  |  |

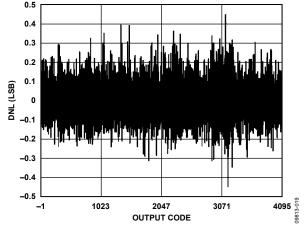

| Differential Nonlinearity (DNL)               | Full |      | ±0.5     |            | LSB   |  |  |

| Integral Nonlinearity (INL)                   | Full |      | ±0.6     |            | LSB   |  |  |

| TEMPERATURE DRIFT                             |      |      |          |            |       |  |  |

| Offset Error                                  | Full |      | 18       |            | μV/°C |  |  |

| Gain Error                                    | Full |      | 0.07     |            | %/°C  |  |  |

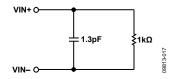

| ANALOG INPUTS (VIN±)                          |      |      |          |            |       |  |  |

| Differential Input Voltage Range <sup>2</sup> | Full | 1.18 | 1.5      | 1.6        | V p-p |  |  |

| Input Common-Mode Voltage                     | Full |      | 1.8      |            | V     |  |  |

| Input Resistance (Differential)               | Full |      | 1        |            | kΩ    |  |  |

| Input Capacitance (Differential)              | 25°C |      | 1.3      |            | pF    |  |  |

| POWER SUPPLY                                  |      |      |          |            |       |  |  |

| AVDD                                          | Full | 1.8  | 1.9      | 2.0        | V     |  |  |

| DRVDD                                         | Full | 1.8  | 1.9      | 2.0        | V     |  |  |

| SPI_VDDIO                                     | Full | 1.8  | 1.9      | 3.3        | V     |  |  |

| Supply Currents                               |      |      |          |            |       |  |  |

| I <sub>AVDD</sub> <sup>3</sup>                | Full |      | 300      | 330        | mA    |  |  |

| I <sub>DRVDD</sub> <sup>3</sup>               | Full |      | 66       | 80         | mA    |  |  |

| Power Dissipation <sup>3</sup>                | Full |      | 695      | 779        | mW    |  |  |

| Power-Down Dissipation                        | Full |      | 15       |            | mW    |  |  |

| Standby Dissipation                           | Full |      | 72       |            | mW    |  |  |

| Standby to Power-Up Time                      | Full |      | 10       |            | μs    |  |  |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions and information about how these tests were completed.

<sup>&</sup>lt;sup>2</sup> The input range is programmable through the SPI, and the range specified reflects the nominal values of each setting. See the SPI Register Map section for additional details.

$<sup>^3</sup>$   $I_{AVDD}$  and  $I_{DRVDD}$  are measured with a -1 dBFS, 30 MHz sine input at a rated sample rate.

#### **AC SPECIFICATIONS**

$AVDD = 1.9 \text{ V}, DRVDD = 1.9 \text{ V}, T_{MIN} = -40 ^{\circ}\text{C}, T_{MAX} = +85 ^{\circ}\text{C}, f_{IN} = -1.0 \text{ dBFS}, full scale} = 1.5 \text{ V}, unless otherwise noted.}$

Table 2.

|                                                                                                  |      |      | AD6641-    | 500        |      |

|--------------------------------------------------------------------------------------------------|------|------|------------|------------|------|

| Parameter <sup>1, 2</sup>                                                                        | Temp | Min  | Тур        | Max        | Unit |

| SNR                                                                                              |      |      |            |            |      |

| $f_{IN} = 30 \text{ MHz}$                                                                        | 25°C |      | 66.0       |            | dBFS |

| $f_{IN} = 125 \text{ MHz}$                                                                       | 25°C |      | 65.9       |            | dBFS |

|                                                                                                  | Full | 65.0 |            |            | dBFS |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C |      | 65.8       |            | dBFS |

| $f_{IN} = 450 \text{ MHz}$                                                                       | 25°C |      | 65.1       |            | dBFS |

| SINAD                                                                                            |      |      |            |            |      |

| $f_{IN} = 30 \text{ MHz}$                                                                        | 25°C |      | 66.0       |            | dBFS |

| $f_{IN} = 125 \text{ MHz}$                                                                       | 25°C |      | 65.7       |            | dBFS |

|                                                                                                  | Full | 63.8 |            |            | dBFS |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C |      | 65.3       |            | dBFS |

| $f_{IN} = 450 \text{ MHz}$                                                                       | 25°C |      | 64.6       |            | dBFS |

| EFFECTIVE NUMBER OF BITS (ENOB)                                                                  |      |      |            |            |      |

| $f_{IN} = 30 \text{ MHz}$                                                                        | 25°C |      | 10.7       |            | Bits |

| f <sub>IN</sub> = 125 MHz                                                                        | 25°C |      | 10.6       |            | Bits |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C |      | 10.5       |            | Bits |

| $f_{\text{IN}} = 450 \text{ MHz}$                                                                | 25°C |      | 10.4       |            | Bits |

| SFDR                                                                                             |      |      |            |            |      |

| $f_{IN} = 30 \text{ MHz}$                                                                        | 25°C |      | 88         |            | dBc  |

| $f_{\text{IN}} = 125 \text{ MHz}$                                                                | 25°C |      | 83         |            | dBc  |

|                                                                                                  | Full | 77   | 03         |            | dBc  |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C | ' '  | 80         |            | dBc  |

| $f_{\text{IN}} = 450 \text{ MHz}$                                                                | 25°C |      | 72         |            | dBc  |

| WORST HARMONIC (SECOND OR THIRD)                                                                 |      |      |            |            | 0.50 |

| $f_{\text{IN}} = 30 \text{ MHz}$                                                                 | 25°C |      | -92        |            | dBc  |

| $f_{\text{IN}} = 125 \text{ MHz}$                                                                | 25°C |      | 72         | <b>–77</b> | dBc  |

|                                                                                                  | Full |      | -84        | ,,         | dBc  |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C |      | -80        |            | dBc  |

| $f_{\text{IN}} = 450 \text{ MHz}$                                                                | 25°C |      | –72        |            | dBc  |

| WORST OTHER HARMONIC (SFDR EXCLUDING SECOND AND THIRD)                                           | 25 C |      | 12         |            | abc  |

| $f_{\text{IN}} = 30 \text{ MHz}$                                                                 | 25°C |      | -90        |            | dBc  |

| $f_{\text{IN}} = 125 \text{ MHz}$                                                                | 25°C |      | -90<br>-90 |            | dBc  |

| 1 N - 123   WILLE                                                                                | Full |      | -30        | <b>–77</b> | dBc  |

| $f_{IN} = 250 \text{ MHz}$                                                                       | 25°C |      | -85        | -//        | dBc  |

| $f_{\text{IN}} = 450 \text{ MHz}$                                                                | 25°C |      | -63<br>-78 |            | dBc  |

| TWO-TONE IMD                                                                                     | 23 C |      | -/0        |            | UDC  |

|                                                                                                  | 25°C |      | 0.3        |            | dDc  |

| $f_{\text{IN1}} = 119.8 \text{ MHz}$ , $f_{\text{IN2}} = 125.8 \text{ MHz}$ (-7 dBFS, Each Tone) | 25°C |      | -82        |            | dBc  |

| ANALOG INPUT BANDWIDTH                                                                           | 25°C |      | 1          |            | GHz  |

<sup>&</sup>lt;sup>1</sup> All ac specifications tested by driving CLK+ and CLK- differentially.

<sup>&</sup>lt;sup>2</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions and information about how these tests were completed.

### **DIGITAL SPECIFICATIONS**

$AVDD = 1.9 \text{ V}, DRVDD = 1.9 \text{ V}, T_{MIN} = -40 ^{\circ}\text{C}, T_{MAX} = +85 ^{\circ}\text{C}, f_{IN} = -1.0 \text{ dBFS}, full scale = 1.5 \text{ V}, unless otherwise noted.}$

Table 3.

|                                                                  |      | AD6641-500       |             |

|------------------------------------------------------------------|------|------------------|-------------|

| Parameter <sup>1</sup>                                           | Temp | Min Typ Max      | Unit        |

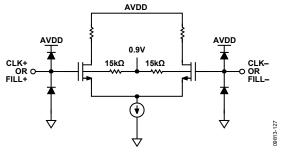

| CLOCK INPUTS (CLK±)                                              |      |                  |             |

| Logic Compliance                                                 | Full | CMOS/LVDS/LVPECL |             |

| Internal Common-Mode Bias                                        | Full | 0.9              | V           |

| Differential Input Voltage                                       |      |                  |             |

| High Level Input (V <sub>IH</sub> )                              | Full | 0.2 1.8          | V p-p       |

| Low Level Input (V <sub>IL</sub> )                               | Full | -1.8 -0.2        |             |

| High Level Input Current (Iℍ)                                    | Full | -10 +10          | μΑ          |

| Low Level Input Current (I <sub>L</sub> )                        | Full | -10 +10          | μΑ          |

| Input Resistance (Differential)                                  | Full | 8 10 12          | kΩ          |

| Input Capacitance                                                | Full | 4                | pF          |

| LOGIC INPUTS (SPI, SPORT)                                        |      |                  | r           |

| Logic Compliance                                                 | Full | CMOS             |             |

| Logic 1 Voltage                                                  | Full | 0.8 × SPI_VDDIO  | V           |

| Logic 0 Voltage                                                  | Full |                  | SPI_VDDIO V |

| Logic 1 Input Current (SDIO)                                     | Full | 0                | μΑ          |

| Logic 0 Input Current (SDIO)                                     | Full | _60              | μΑ          |

| Logic 1 Input Current (SCLK)                                     | Full | 50               | μΑ          |

| Logic 0 Input Current (SCLK)                                     | Full | 0                | μΑ          |

| Input Capacitance                                                | 25℃  | 4                | pF          |

| LOGIC INPUTS (DUMP, CSB)                                         | 25 C | ·                | Pi          |

| Logic Compliance                                                 | Full | CMOS             |             |

| Logic 1 Voltage                                                  | Full | 0.8 × DRVDD      | V           |

| Logic 0 Voltage                                                  | Full |                  | CDRVDD V    |

| Logic 1 Input Current                                            | Full | 0.2 ^            | μA          |

| Logic 0 Input Current                                            | Full | _60              | μΑ          |

| Input Capacitance                                                | 25°C | 4                | pF          |

| LOGIC INPUTS (FILL±)                                             | 23 C | 7                | Pi          |

| Logic Compliance                                                 | Full | CMOS/LVDS/LVPECL |             |

| Internal Common-Mode Bias                                        | Full | 0.9              | V           |

|                                                                  | Full | 0.9              | V           |

| Differential Input Voltage<br>High Level Input (V <sub>H</sub> ) | Full | 0.2              | V           |

| ·                                                                |      | 0.2              | V p-p       |

| Low Level Input (V <sub>IL</sub> )                               | Full | -1.8 -0.2        | ' '         |

| High Level Input Current (I <sub>IH</sub> )                      | Full | -10 +10          | μΑ          |

| Low Level Input Current (I <sub>IL</sub> )                       | Full | -10 +10          | μA          |

| Input Resistance (Differential)                                  | Full | 8 10 12          | kΩ          |

| Input Capacitance                                                | Full | 4                | pF          |

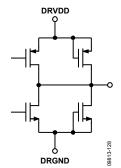

| LOGIC OUTPUTS <sup>2</sup> (FULL, EMPTY)                         |      |                  |             |

| Logic Compliance                                                 | Full | CMOS             |             |

| High Level Output Voltage                                        | Full | DRVDD - 0.05     | V           |

| Low Level Output Voltage                                         | Full | DRG              | ND + 0.05 V |

| LOGIC OUTPUTS <sup>2</sup> (SPI, SPORT)                          |      |                  |             |

| Logic Compliance                                                 | Full | CMOS             |             |

| High Level Output Voltage                                        | Full | SPI_VDDIO – 0.05 | V           |

| Low Level Output Voltage                                         | Full | DRG              | ND + 0.05 V |

|                                        |      |              | AD6641-5           | 00                         |      |

|----------------------------------------|------|--------------|--------------------|----------------------------|------|

| Parameter <sup>1</sup>                 | Temp | Min          | Тур                | Max                        | Unit |

| LOGIC OUTPUTS                          |      |              |                    |                            |      |

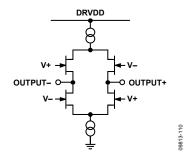

| DDR LVDS Mode (PCLK±, PD[5:0]±, PDOR±) |      |              |                    |                            |      |

| Logic Compliance                       | Full |              | LVDS               |                            |      |

| Vod Differential Output Voltage        | Full | 247          |                    | 454                        | mV   |

| Vos Output Offset Voltage              | Full | 1.125        |                    | 1.375                      | V    |

| Parallel CMOS Mode (PCLK±, PD[11:0])   |      |              |                    |                            |      |

| Logic Compliance                       | Full |              | CMOS               |                            |      |

| High Level Output Voltage              | Full | DRVDD - 0.05 |                    |                            | V    |

| Low Level Output Voltage               | Full |              |                    | DRGND + 0.05               | V    |

| Output Coding                          |      | Twos complem | nent, Gray code, c | or offset binary (default) |      |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were completed. <sup>2</sup> 5 pF loading.

#### **SWITCHING SPECIFICATIONS**

$AVDD = 1.9 \text{ V}, DRVDD = 1.9 \text{ V}, T_{MIN} = -40 ^{\circ}\text{C}, T_{MAX} = +85 ^{\circ}\text{C}, f_{IN} = -1.0 \text{ dBFS}, full scale} = 1.5 \text{ V}, unless otherwise noted.}$

Table 4.

|                                                                                                            |      | AD6641-500 |      |     |        |

|------------------------------------------------------------------------------------------------------------|------|------------|------|-----|--------|

| Parameter <sup>1</sup>                                                                                     | Temp | Min        | Тур  | Max | Unit   |

| OUTPUT DATA RATE                                                                                           |      |            |      |     |        |

| Maximum Output Data Rate (Decimate by 8 at 500 MSPS Sample Rate, Parallel CMOS or DDR LVDS Mode Interface) | Full | 62.5       |      |     | MHz    |

| Maximum Output Data Rate (Decimate by 8 at 500 MSPS Sample Rate, SPORT Mode)                               | Full | 62.5       |      |     | MHz    |

| PULSE WIDTH/PERIOD (CLK±)                                                                                  |      |            |      |     |        |

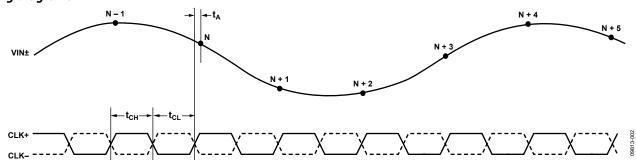

| CLK± Pulse Width High (tcH)                                                                                | Full |            | 1    |     | ns     |

| CLK± Pulse Width Low (t <sub>CL</sub> )                                                                    | Full |            | 1    |     | ns     |

| Rise Time (t <sub>R</sub> ) (20% to 80%)                                                                   | 25°C |            | 0.2  |     | ns     |

| Fall Time (t <sub>F</sub> ) (20% to 80%)                                                                   | 25°C |            | 0.2  |     | ns     |

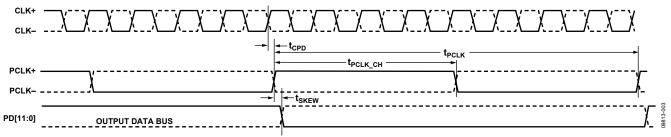

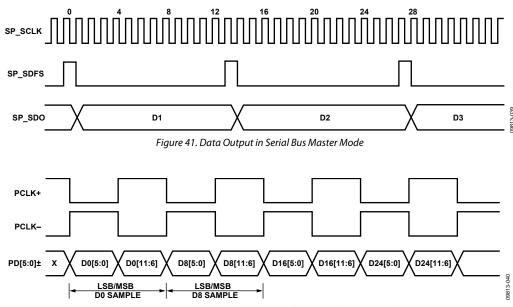

| PULSE WIDTH/PERIOD (PCLK±, DDR LVDS MODE)                                                                  |      |            |      |     |        |

| PCLK± Pulse Width High (t <sub>PCLK_CH</sub> )                                                             | Full |            | 8    |     | ns     |

| PCLK± Period (t <sub>PCLK</sub> )                                                                          | Full |            | 16   |     | ns     |

| Propagation Delay (t <sub>CPD</sub> , CLK± to PCLK±)                                                       | Full |            | ±0.1 |     | ns     |

| Rise Time (t <sub>R</sub> ) (20% to 80%)                                                                   | 25°C |            | 0.2  |     | ns     |

| Fall Time (t <sub>F</sub> ) (20% to 80%)                                                                   | 25°C |            | 0.2  |     | ns     |

| Data to PCLK Skew (t <sub>skew</sub> )                                                                     | Full |            | 0.2  |     | ns     |

| SERIAL PORT OUTPUT TIMING <sup>2</sup>                                                                     |      |            |      |     |        |

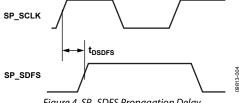

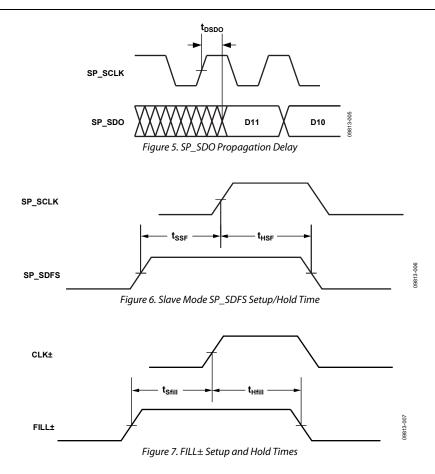

| SP_SDFS Propagation Delay (t <sub>DSDFS</sub> )                                                            | Full |            | 3    |     | ns     |

| SP_SDO Propagation Delay (t <sub>DSDO</sub> )                                                              | Full |            | 3    |     | ns     |

| SERIAL PORT INPUT TIMING                                                                                   |      |            |      |     |        |

| SP_SDFS Setup Time (t <sub>SSF</sub> )                                                                     | Full |            | 2    |     | ns     |

| SP_SDFS Hold Time (t <sub>HSF</sub> )                                                                      | Full |            | 2    |     | ns     |

| FILL± INPUT TIMING                                                                                         |      |            |      |     |        |

| FILL± Setup Time (tsfill)                                                                                  | Full |            | 0.5  |     | ns     |

| FILL± Hold Time (t <sub>Hfill</sub> )                                                                      | Full |            | 0.7  |     | ns     |

| APERTURE DELAY (t <sub>A</sub> )                                                                           | 25°C |            | 0.85 |     | ns     |

| APERTURE UNCERTAINTY (JITTER, t <sub>J</sub> )                                                             | 25°C |            | 80   |     | fs rms |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and information about how these tests were completed. <sup>2</sup> 5 pF loading.

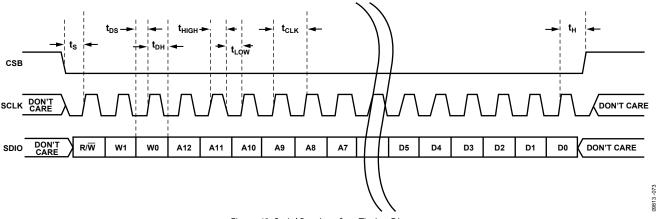

### **SPI TIMING REQUIREMENTS**

Table 5.

| Parameter             | Description                                                                                           | Limit | Unit   |

|-----------------------|-------------------------------------------------------------------------------------------------------|-------|--------|

| t <sub>DS</sub>       | Setup time between the data and the rising edge of SCLK                                               | 2     | ns min |

| $t_{DH}$              | Hold time between the data and the rising edge of SCLK                                                | 2     | ns min |

| t <sub>CLK</sub>      | Period of the SCLK                                                                                    | 40    | ns min |

| $t_{S}$               | Setup time between CSB and SCLK                                                                       | 2     | ns min |

| tн                    | Hold time between CSB and SCLK                                                                        | 2     | ns min |

| t <sub>HIGH</sub>     | SCLK pulse width high                                                                                 | 10    | ns min |

| t <sub>LOW</sub>      | SCLK pulse width low                                                                                  | 10    | ns min |

| t <sub>EN_SDIO</sub>  | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge | 10    | ns min |

| t <sub>DIS_SDIO</sub> | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge  | 10    | ns min |

### **Timing Diagrams**

Figure 2. Input Interface Timing

Figure 3. Parallel CMOS Mode Output Interface Timing

Figure 4. SP\_SDFS Propagation Delay

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

|                             | T                           |

|-----------------------------|-----------------------------|

| Parameter                   | Rating                      |

| Electrical                  |                             |

| AVDD to AGND                | −0.3 V to +2.0 V            |

| DRVDD to DRGND              | −0.3 V to +2.0 V            |

| AGND to DRGND               | −0.3 V to +0.3 V            |

| AVDD to DRVDD               | -2.0 V to +2.0 V            |

| SPI_VDDIO to AVDD           | −2.0 V to +2.0 V            |

| SPI_VDDIO to DRVDD          | -2.0 V to +2.0 V            |

| PD[5:0]± to DRGND           | -0.3 V to DRVDD + 0.2 V     |

| PCLK± to DRGND              | -0.3 V to DRVDD + 0.2 V     |

| PDOR± to DRGND              | -0.3 V to DRVDD + 0.2 V     |

| FULL to DRGND               | -0.3 V to DRVDD + 0.2 V     |

| CLK± to AGND                | −0.3 V to AVDD + 0.2 V      |

| FILL± to AGND               | −0.3 V to DRVDD + 0.2 V     |

| DUMP to AGND                | −0.3 V to DRVDD + 0.2 V     |

| EMPTY to AGND               | −0.3 V to DRVDD + 0.2 V     |

| VIN± to AGND                | −0.3 V to AVDD + 0.2 V      |

| VREF to AGND                | −0.3 V to AVDD + 0.2 V      |

| CML to AGND                 | −0.3 V to AVDD + 0.2 V      |

| CSB to DRGND                | -0.3 V to SPI_VDDIO + 0.3 V |

| SP_SCLK, SP_SDFS to AGND    | -0.3 V to SPI_VDDIO + 0.3 V |

| SDIO to DRGND               | -0.3 V to SPI_VDDIO + 0.3 V |

| SP_SDO to DRGND             | -0.3 V to SPI_VDDIO + 0.3 V |

| Environmental               |                             |

| Storage Temperature Range   | −65°C to +125°C             |

| Operating Temperature Range | −40°C to +85°C              |

| Lead Temperature            | 300°C                       |

| (Soldering, 10 sec)         |                             |

| Junction Temperature        | 150°C                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

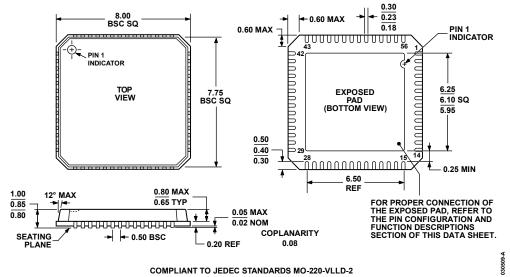

#### THERMAL RESISTANCE

The exposed pad must be soldered to the ground plane for the LFCSP package. Soldering the exposed pad to the PCB increases the reliability of the solder joints, maximizing the thermal capability of the package.

Table 7.

| Package Type               | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|----------------------------|---------------|-----------------|------|

| 56-Lead LFCSP_VQ (CP-56-1) | 23.7          | 1.7             | °C/W |

Typical  $\theta_{JA}$  and  $\theta_{JC}$  are specified for a 4-layer board in still air. Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{JA}$ .

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

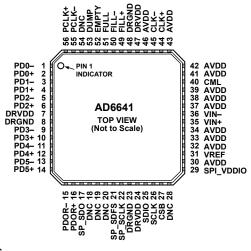

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

- NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD IS THE ONLY ANALOG GROUND

CONNECTION FOR THE CHIP. IT MUST BE CONNECTED TO PCB AGND.

Figure 8. Pin Configuration for DDR LVDS Mode

**Table 8. DDR LVDS Mode Pin Function Descriptions**

| Pin No.                                       | Mnemonic  | Description                                                                                                     |

|-----------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------|

| 0                                             | EPAD      | Exposed Pad. The exposed pad is the only ground connection for the chip. The pad must be connected to PCB AGND. |

| 1                                             | PD0-      | PD0 Data Output (LSB)—Complement.                                                                               |

| 2                                             | PD0+      | PD0 Data Output (LSB)—True.                                                                                     |

| 3                                             | PD1-      | PD1 Data Output—Complement.                                                                                     |

| 4                                             | PD1+      | PD1 Data Output—True.                                                                                           |

| 5                                             | PD2-      | PD2 Data Output—Complement.                                                                                     |

| 6                                             | PD2+      | PD2 Data Output—True.                                                                                           |

| 7, 24, 47                                     | DRVDD     | 1.9 V Digital Output Supply.                                                                                    |

| 8, 23, 48                                     | DRGND     | Digital Output Ground.                                                                                          |

| 9                                             | PD3-      | PD3 Data Output—Complement.                                                                                     |

| 10                                            | PD3+      | PD3 Data Output—True.                                                                                           |

| 11                                            | PD4-      | PD4 Data Output—Complement.                                                                                     |

| 12                                            | PD4+      | PD4 Data Output—True.                                                                                           |

| 13                                            | PD5-      | PD5 Data Output (MSB)—Complement.                                                                               |

| 14                                            | PD5+      | PD5 Data Output (MSB)—True.                                                                                     |

| 15                                            | PDOR-     | Overrange Output—Complement.                                                                                    |

| 16                                            | PDOR+     | Overrange Output—True.                                                                                          |

| 17                                            | SP_SDO    | SPORT Output.                                                                                                   |

| 18, 19, 20, 28, 54                            | DNC       | Do Not Connect. Do not connect to this pin.                                                                     |

| 21                                            | SP_SDFS   | SPORT Frame Sync Input (Slave Mode)/Output (Master Mode).                                                       |

| 22                                            | SP_SCLK   | SPORT Clock Input (Slave Mode)/Output (Master Mode).                                                            |

| 25                                            | SDIO      | Serial Port Interface (SPI) Data Input/Output (Serial Port Mode).                                               |

| 26                                            | SCLK      | Serial Port Interface Clock (Serial Port Mode).                                                                 |

| 27                                            | CSB       | Serial Port Chip Select (Active Low).                                                                           |

| 29                                            | SPI_VDDIO | 1.9 V or 3.3 V SPI I/O Supply.                                                                                  |

| 30, 32, 33, 34, 37, 38, 39,<br>41, 42, 43, 46 | AVDD      | 1.9 V Analog Supply.                                                                                            |

| 31                                            | VREF      | Voltage Reference Input/Output. Nominally 0.75 V.                                                               |

| 35                                            | VIN+      | Analog Input—True.                                                                                              |

| 36                                            | VIN-      | Analog Input—Complement.                                                                                        |

| Pin No. | Mnemonic | Description                                                                                                                           |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 40      | CML      | Common-Mode Output. Enabled through the SPI, this pin provides a reference for the optimized internal bias voltage for VIN+ and VIN–. |

| 44      | CLK+     | Clock Input—True.                                                                                                                     |

| 45      | CLK-     | Clock Input—Complement.                                                                                                               |

| 49      | FILL+    | FIFO Fill Input (LVDS)—True.                                                                                                          |

| 50      | FILL-    | FIFO Fill Input (LVDS)—Complement.                                                                                                    |

| 51      | FULL     | FIFO Full Output Indicator.                                                                                                           |

| 52      | EMPTY    | FIFO Empty Output Indicator.                                                                                                          |

| 53      | DUMP     | FIFO Readback Input.                                                                                                                  |

| 55      | PCLK-    | Data Clock Output—Complement.                                                                                                         |

| 56      | PCLK+    | Data Clock Output—True.                                                                                                               |

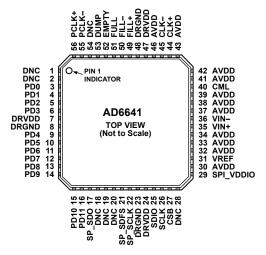

- 1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD IS THE ONLY ANALOG GROUND

CONNECTION FOR THE CHIP. IT MUST BE CONNECTED TO PCB AGND.

Figure 9. Pin Configuration for Parallel CMOS Mode

**Table 9. Parallel CMOS Mode Pin Function Descriptions**

| Pin No.                                       | Mnemonic  | Description                                                                                                                           |

|-----------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0                                             | EPAD      | Exposed Pad. The exposed pad is the only ground connection for the chip. The pad must be connected to PCB AGND.                       |

| 1, 2, 18, 19, 20, 28, 54                      | DNC       | Do Not Connect. Do not connect to this pin.                                                                                           |

| 3                                             | PD0       | PD0 Data Output.                                                                                                                      |

| 4                                             | PD1       | PD1 Data Output.                                                                                                                      |

| 5                                             | PD2       | PD2 Data Output.                                                                                                                      |

| 6                                             | PD3       | PD3 Data Output.                                                                                                                      |

| 7, 24, 47                                     | DRVDD     | 1.9 V Digital Output Supply.                                                                                                          |

| 8, 23, 48                                     | DRGND     | Digital Output Ground.                                                                                                                |

| 9                                             | PD4       | PD4 Data Output.                                                                                                                      |

| 10                                            | PD5       | PD5 Data Output.                                                                                                                      |

| 11                                            | PD6       | PD6 Data Output.                                                                                                                      |

| 12                                            | PD7       | PD7 Data Output.                                                                                                                      |

| 13                                            | PD8       | PD8 Data Output.                                                                                                                      |

| 14                                            | PD9       | PD9 Data Output.                                                                                                                      |

| 15                                            | PD10      | PD10 Data Output.                                                                                                                     |

| 16                                            | PD11      | PD11 Data Output (MSB).                                                                                                               |

| 17                                            | SP_SDO    | SPORT Output.                                                                                                                         |

| 21                                            | SP_SDFS   | SPORT Frame Sync Input (Slave Mode)/Output (Master Mode).                                                                             |

| 22                                            | SP_SCLK   | SPORT Clock Input (Slave Mode)/Output (Master Mode).                                                                                  |

| 25                                            | SDIO      | Serial Port Interface (SPI) Data Input/Output (Serial Port Mode).                                                                     |

| 26                                            | SCLK      | Serial Port Interface Clock (Serial Port Mode).                                                                                       |

| 27                                            | CSB       | Serial Port Chip Select (Active Low).                                                                                                 |

| 29                                            | SPI_VDDIO | 1.9 V or 3.3 V SPI I/O Supply.                                                                                                        |

| 30, 32, 33, 34, 37, 38, 39,<br>41, 42, 43, 46 | AVDD      | 1.9 V Analog Supply.                                                                                                                  |

| 31                                            | VREF      | Voltage Reference Input/Output. Nominally 0.75 V.                                                                                     |

| 35                                            | VIN+      | Analog Input—True.                                                                                                                    |

| 36                                            | VIN-      | Analog Input—Complement.                                                                                                              |

| 40                                            | CML       | Common-Mode Output. Enabled through the SPI, this pin provides a reference for the optimized internal bias voltage for VIN+ and VIN–. |

| 44                                            | CLK+      | Clock Input—True.                                                                                                                     |

| Pin No. | Mnemonic | Description                        |

|---------|----------|------------------------------------|

| 45      | CLK-     | Clock Input—Complement.            |

| 49      | FILL+    | FIFO Fill Input (LVDS)—True.       |

| 50      | FILL-    | FIFO Fill Input (LVDS)—Complement. |

| 51      | FULL     | FIFO Full Output Indicator.        |

| 52      | EMPTY    | FIFO Empty Output Indicator.       |

| 53      | DUMP     | FIFO Readback Input.               |

| 55      | PCLK-    | Data Clock Output—Complement.      |

| 56      | PCLK+    | Data Clock Output—True.            |

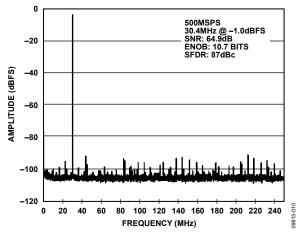

### TYPICAL PERFORMANCE CHARACTERISTICS

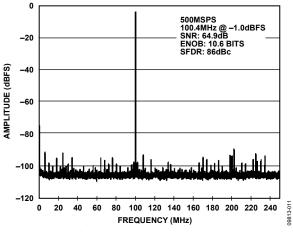

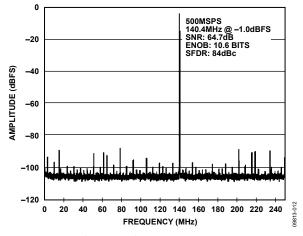

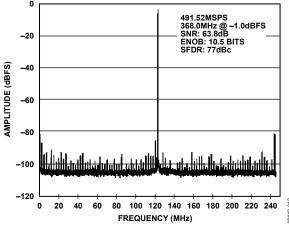

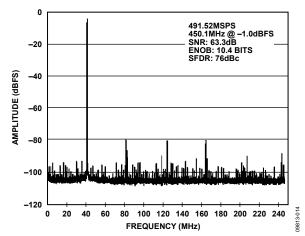

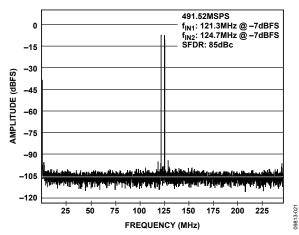

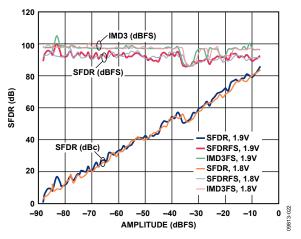

AVDD = 1.9 V, DRVDD = 1.9 V, rated sample rate,  $T_A = 25^{\circ}$ C, 1.5 V p-p differential input,  $A_{\rm IN} = -1$  dBFS, unless otherwise noted.

Figure 10. 16k Point Single-Tone FFT; 500 MSPS, 30.4 MHz

Figure 11. 16k Point Single-Tone FFT; 500 MSPS, 100.4 MHz

Figure 12. 16k Point Single-Tone FFT; 500 MSPS, 140.4 MHz

Figure 13. 16k Point Single-Tone FFT; 491.52 MSPS, 368.0 MHz

Figure 14. 16k Point Single-Tone FFT; 491.52 MSPS, 450.1 MHz

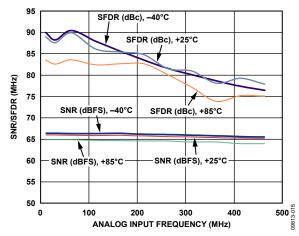

Figure 15. Single-Tone SNR/SFDR vs. Input Frequency ( $f_{\rm IN}$ ) and Temperature; 500 MSPS

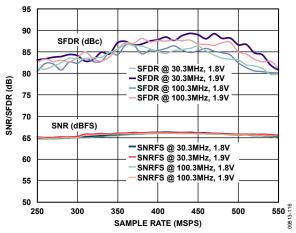

Figure 16. SNR/SFDR vs. Sample Rate and Supply

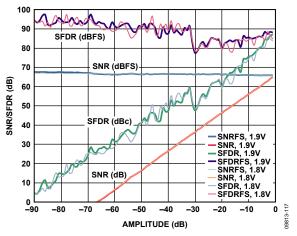

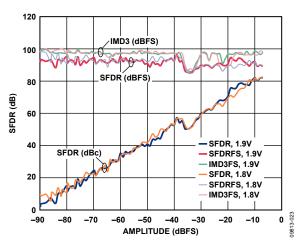

Figure 17. SNR/SFDR vs. Input Amplitude; 500 MSPS,140.3 MHz

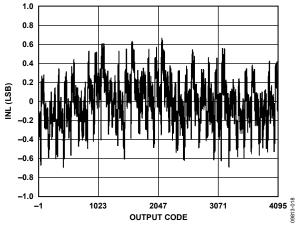

Figure 18. INL; 500 MSPS

Figure 19. DNL; 500 MSPS

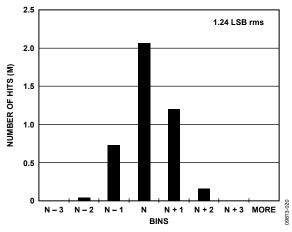

Figure 20. Grounded Input Histogram; 500 MSPS

Figure 21. 16k Point Single-Tone FFT; 491.52 MSPS,  $f_{\rm IN1}=121.3$  MHz,  $f_{\rm IN2}=124.7$  MHz

Figure 22. Two-Tone SFDR vs. Input Amplitude; 500 MSPS, 119.2 MHz, 122.5 MHz

Figure 23. Two-Tone SFDR vs. Input Amplitude; 500 MSPS, 139.3 MHz, 141.3 MHz

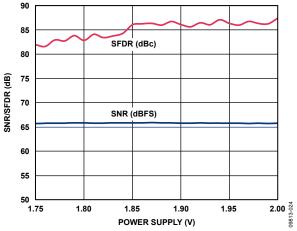

Figure 24. SNR/SFDR vs. Power Supply

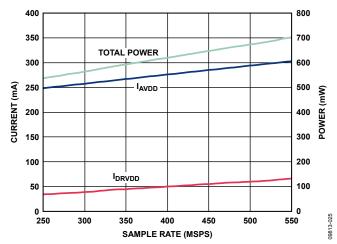

Figure 25. Current and Power vs. Sample Rate

### **EQUIVALENT CIRCUITS**

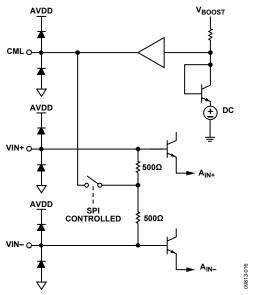

Figure 26. DC Equivalent Analog Input Circuit

Figure 27. AC Equivalent Analog Input Circuit

Figure 28. Equivalent CLK± and FILL± Input Circuit

Figure 29. Equivalent PD[11:0], FULL, EMPTY, PCLK±, and SP\_SDO Output Circuit

Figure 30. LVDS Outputs (PDOR±, PD[5:0]±, PCLK±)

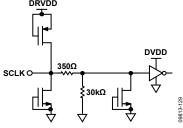

Figure 31. Equivalent SCLK Input Circuit

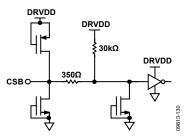

Figure 32. Equivalent CSB Input Circuit

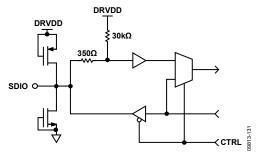

Figure 33. Equivalent SDIO Circuit

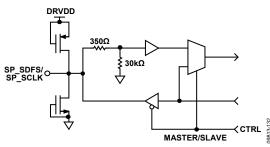

Figure 34. Equivalent SP\_SDFS and SP\_SCLK Circuit

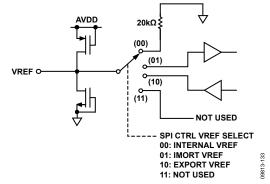

Figure 35. Equivalent VREF Circuit

# **SPI REGISTER MAP**

Table 10. Memory Map Register

| Addr.<br>(Hex) | Parameter Name        | Bit 7<br>(MSB)                       | Bit 6                                                                     | Bit 5                                                   | Bit 4                                                  | Bit 3                                                                                                                                                                                                                                                                                                              | Bit 2                                               | Bit 1                                                      | Bit 0<br>(LSB)                                                              | Default<br>Value<br>(Hex) | Default<br>Notes/<br>Comments                                                                                                                                 |

|----------------|-----------------------|--------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | nfiguration Registers | ,                                    | 1                                                                         |                                                         | II.                                                    |                                                                                                                                                                                                                                                                                                                    | ı                                                   | 1                                                          | ,                                                                           | 1 . ,                     |                                                                                                                                                               |

| 0x00           | CHIP_PORT_CONFIG      | 0                                    | LSB<br>first                                                              | Soft<br>reset                                           | 1                                                      | 1                                                                                                                                                                                                                                                                                                                  | Soft<br>reset                                       | LSB first                                                  | 0                                                                           | 0x18                      | The nibbles should be mirrored by the user so that LSB or MSB first mode registers correctly, regardless of shift mode.                                       |

| 0x01           | CHIP_ID               |                                      | 8-bit chip ID, Bits[7:0] = 0xA0                                           |                                                         |                                                        |                                                                                                                                                                                                                                                                                                                    |                                                     |                                                            |                                                                             |                           | Default is<br>unique chip<br>ID, different<br>for each<br>device. This is<br>a read-only<br>register.                                                         |

| 0x02           | CHIP_GRADE            | 0                                    | 0                                                                         |                                                         | Speed grade: X1 X1 X1 X1 X1 X1                         |                                                                                                                                                                                                                                                                                                                    |                                                     |                                                            | X <sup>1</sup>                                                              | Read<br>only              | Child ID<br>used to<br>differentiate<br>graded<br>devices.                                                                                                    |

|                | Register              | 1                                    |                                                                           |                                                         |                                                        |                                                                                                                                                                                                                                                                                                                    |                                                     |                                                            | _                                                                           | 0x00                      |                                                                                                                                                               |

| 0xFF           | DEVICE_UPDATE         |                                      | [7:1] = 0000000 SW transfer                                               |                                                         |                                                        |                                                                                                                                                                                                                                                                                                                    |                                                     |                                                            |                                                                             |                           | Synchro-<br>nously<br>transfers data<br>from the<br>master shift<br>register to the<br>slave.                                                                 |

| ADC Fu         | nctions               |                                      |                                                                           |                                                         |                                                        |                                                                                                                                                                                                                                                                                                                    |                                                     |                                                            |                                                                             |                           |                                                                                                                                                               |

| 0x08           | Modes                 | 0                                    | 0                                                                         | 0                                                       | 0                                                      | 0 Internal power-down mode:<br>000 = normal (power-up, default)<br>001 = full power-down<br>010 = standby<br>011 = reserved                                                                                                                                                                                        |                                                     |                                                            |                                                                             | 0x00                      | Determines various generic modes of chip operation.                                                                                                           |

| 0x0D           | TEST_IO               | Patte<br>10 = t<br>Pattern<br>11 = t | only, set = 1000) ern 1 only oggle ern 1/ ern 2 oggle 1/0000 oggle ern 1/ | Reset<br>PN23<br>gen:<br>1 = on<br>0 = off<br>(default) | Reset<br>PN9<br>gen: 1 =<br>on<br>0 = off<br>(default) | Output test mode:  0000 = off (default)  0001 = midscale short  0010 = +FS short  0011 = -FS short  0100 = checkerboard output  0101 = PN23 sequence  0110 = PN9  0111 = one/zero word toggle  1000 = user defined  1001 = unused  1010 = unused  1011 = unused  1010 = unused  (format determined by OUTPUT_MODE) |                                                     |                                                            |                                                                             | 0x00                      | When set, the test data is placed on the output pins in place of normal data. Set pattern values: Pattern 1: Reg 0x19, Reg 0x1A Pattern 2: Reg 0x1B Reg 0x1C. |

| 0x14           | OUTPUT_MODE           | 0                                    | 0                                                                         | 0                                                       | Output disable: 0 = enable (default) 1 = disable       | 0 =<br>CMOS:<br>1 =<br>LVDS<br>(default)                                                                                                                                                                                                                                                                           | Output<br>invert:<br>1 = on<br>0 = off<br>(default) | Data form<br>00 = offs<br>(def<br>01 =<br>compl<br>10 = Gr | nat select:<br>set binary<br>ault)<br>twos<br>lement<br>ray code<br>eserved | 0x08                      |                                                                                                                                                               |

| Addr.<br>(Hex)      | Darameter Name               | Bit 7<br>(MSB)                                         | Bit 6                                                    | Bit 5       | Bit 4        | Bit 3            | Bit 2                                                                                                                                              | Bit 1                          | Bit 0<br>(LSB) | Default<br>Value             | Default<br>Notes/<br>Comments                                                                                                            |

|---------------------|------------------------------|--------------------------------------------------------|----------------------------------------------------------|-------------|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| <b>нех)</b><br>0х15 | Parameter Name OUTPUT_ADJUST | (M2R)                                                  |                                                          |             | BIT 4        | LVDS             |                                                                                                                                                    |                                |                | ( <b>Hex</b> )               | Comments                                                                                                                                 |

| 7. 1. 3             | 0011 01_AD3031               |                                                        | [7:4] = 0000 LVDS LVDS fine adjust: course 001 = 3.50 mA |             |              |                  |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | adjust:          |                                                                                                                                                    | 010 = 3.25  m                  |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | 0 =              |                                                                                                                                                    | 011 = 3.00 m                   |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | 3.5 mA           |                                                                                                                                                    | 100 = 2.75  m                  |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | (default)<br>1 = |                                                                                                                                                    | 101 = 2.50  m<br>110 = 2.25  m |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | 2.0 mA           |                                                                                                                                                    | 110 = 2.23  m<br>111 = 2.00  m |                |                              |                                                                                                                                          |

| 0x16                | OUTPUT_PHASE                 | Output                                                 |                                                          |             |              | [6:0] = 00000    |                                                                                                                                                    |                                |                | 0x03                         |                                                                                                                                          |

| OX10                | GOTT OT_TIME                 | clock<br>polarity:<br>1 =<br>inverted<br>0 =<br>normal | clock polarity: 1 = inverted 0 =                         |             |              |                  |                                                                                                                                                    |                                | GXG3           |                              |                                                                                                                                          |

|                     |                              | (default)                                              |                                                          |             |              |                  |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

| 0x17                | OUTPUT_DELAY                 | 0                                                      | 0                                                        | 0           | 0            |                  | Output                                                                                                                                             | lock delay:                    |                | 0                            | Shown as                                                                                                                                 |

|                     |                              |                                                        |                                                          |             |              |                  | 0000 = 0 $0001 = -1/10$ $0010 = -2/10$ $0011 = -3/10$ $0100 = reserved$ $0101 = +5/10$ $0110 = +4/10$ $0111 = +3/10$ $1000 = +2/10$ $1001 = +1/10$ |                                |                |                              | fractional<br>value of<br>sampling<br>clock period<br>that is<br>subtracted o<br>added to<br>initial t <sub>SKEW</sub> ,<br>see Figure 3 |

| 0x18                | Input range                  |                                                        | VREF select: 0 Input voltage range setting (V):          |             |              |                  |                                                                                                                                                    |                                |                | 0                            |                                                                                                                                          |

|                     |                              | 00 = inte                                              |                                                          |             |              | 11100 = 1.60     |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

|                     |                              | $(20 \text{ k}\Omega \text{ pu})$<br>01 = imp          |                                                          |             | 11101 = 1.58 |                  |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

|                     |                              | (0.59 V to                                             |                                                          |             |              | 11110 = 1.55     |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

|                     |                              | VREF                                                   |                                                          |             |              |                  | 111111 = 1.5<br>00000 = 1.5                                                                                                                        |                                |                |                              |                                                                                                                                          |

|                     |                              | 10 = exp                                               | ort V <sub>REF</sub>                                     |             |              |                  | 00000 = 1.3<br>00001 = 1.4                                                                                                                         |                                |                |                              |                                                                                                                                          |

|                     |                              | 11= no                                                 | t used                                                   |             |              |                  | 00001 = 1.4<br>00010 = 1.4                                                                                                                         |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              |                  | 00010 = 1.4 $00011 = 1.4$                                                                                                                          |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              | 00100 = 1.39     |                                                                                                                                                    |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              |                  | 00101 = 1.3                                                                                                                                        |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              |                  | 00110 = 1.3                                                                                                                                        |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              |                  | 00111 = 1.3                                                                                                                                        |                                |                |                              |                                                                                                                                          |

|                     |                              |                                                        |                                                          |             |              |                  | 01000 = 1.2                                                                                                                                        | 28                             |                |                              |                                                                                                                                          |